Data centrum migrationis ad DDR5 plus aliis upgrades esse potest.Sed multi vage iustus putant DDR5 transitum ad penitus reponere DDR4.Processores inevitabiliter mutantur in adventu DDR5, et aliquam novam habebuntmemoriainterfaces, sicut patet in prioribus generationibus DRAM upgrades ex SDRAM toDDR4.

Autem, DDR5 interface non est mutatio, ratio processus memoriae ratio mutatur.Re quidem vera mutationes DDR5 ad suggestum servientis compatibile sufficiens iustificare potest.

Cur novam memoriam instrumenti?

Problemata computatione magis implicata ab adventu computatorum creverunt, et hoc inevitabile incrementum evolutionem impulit in forma plurium ministrantium, memoria semper crescens ac facultates repositas, ac superior processus horologii velocitates et nucleus comitum, sed etiam mutationes architecturae mittentes. , inter recentes adoptionis artes disaggregatas et perficiendas AI.

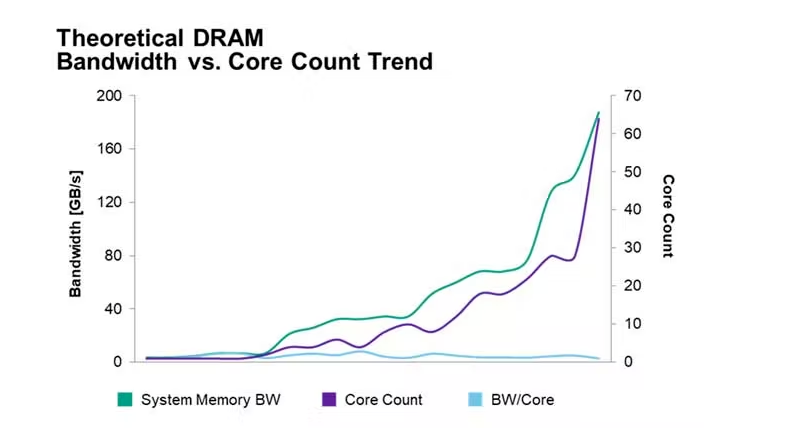

Possent aliqui putare haec omnia tandem fieri quia omnes numeri ascendunt.Tamen, cum numerus nucleorum processuum auctus est, band latitudo DDR gressum non servavit, sed latitudo per nucleum reapse decrescit.

Cum notitia copiae aucta sunt, praesertim HPC, ludi, video coding, apparatus discendi ratiocinandi, magnae analyseos, et databases, licet fasciae memoriae transferre possunt meliores canales ad CPU addendo, Sed hoc plus virtutis consumit. .Processus clavus computat etiam sustentationem accessus limitat, et numerus canalium in perpetuum augeri non potest.

Nonnullae applicationes, praesertim subsystems altae, ut GPUs et processuum speciales AI processuum, altae sedis memoriae typum utuntur (HBM).technicae notitias decurrit a renatis DRAM chippis ad processus per 1024 frenum memoriae vicos, faciens magnam solutionem applicationum scientificorum intensivarum sicut AI.In his applicationibus processus ac memoria necesse est ut quam proxime ad celeriter translationes providendum sit.Sed etiam magis carus est, ac astulae in reponendarum modulorum / upgradabilium modulis aptare non possunt.

Et memoria DDR5, quae hoc anno late evolvi incepit, destinatur ad meliorem canalem latitudinem inter processus et memoriam, dum adhuc upgradeability sustinens.

Sed et latency

Rate translatio DDR5 celerior est quam ulla generationis DDR praecedentis, re vera ad DDR4 comparata, rate translatio DDR5 plus quam dupla est.DDR5 insuper mutationes architecturae additas inducit ut perficiendi in his rates transferendis in quaestus simplices fiant et efficientiam notitiarum observatarum meliorem efficiant.

Accedit longitudo ruptis ab BL8 ad BL16 geminata, permittens singulas modulos habere duos canales independentes et per se duplicare canales in systemate promptos.Non solum celeritates translationis superiores accipis, sed etiam canalem memoriae reaedificatum possides qui DDR4 etiam sine rates translationis superiores efficit.

Processus memoriae intensivae videbunt ingentem boosttionem ex transitu ad DDR5, et multae intensiva notitiarum hodiernarum, praesertim AI, databases, et in negotio processus online (OLTP), apta huic descriptioni.

Etiam magna ipsum.Praesens celeritas amplitudinis DDR5 memoriae est 4800~6400MT/s.Sicut technologia crescit, rate transmissio altior esse expectatur.

Energy consummatio

DDR5 inferiore intentione quam DDR4 utitur, id est 1.1V loco 1.2V.Dum differentia 8% non multum sonat, differentia apparet cum quadrat ad rationem potentiae consumptionis, ie 1.1²/1.2² = 85%, quae ad 15% excepta in rogationibus electricitatis vertit.

Mutationes architecturae ab DDR5 optimize inductae sed efficientiae et rates transferendi superiores, tamen hi numeri difficile sunt quantitare sine mensura accurata applicationis ambitus in qua technologiae adhibetur.Sed tunc rursus, propter meliorem architecturae et rates translationis superiores, finis user emendationem energiae per aliquantulus of data percipiet.

Praeterea, modulus DIMM potest etiam per se ipsam intentionem accommodare, quae necessitatem adaptandi potentiae matricis supplere potest, eo quod additos effectus energiae salutaris praebeat.

Pro centris notitiarum, quanta vis ministrantis consumit et quantum ad refrigerandum impensas attinet, et cum haec considerantur, DDR5 quasi modulus acrius efficax profecto ratio esse potest ad upgrade.

Error correctionis

DDR5 etiam emendationem erroris insculpit et sicut processuum DRAM reformidare pergunt, multi utentes solliciti sunt de errore rate simplici et altiore notitiae integritatis augendo.

Pro servo applicationes, in chip ECC errata simplicia corrigit in lege mandata antequam outputing data ex DDR5.Haec onera nonnulla onera ECC ex algorithmo systematis correctionis ad DRAM ad onus systematis redigendum.

DDR5 etiam errorem recognitionis et sanitizationis inducit, et, si paravit, cogitationes DRAM leget notitias internas et datas emendatas rescribere.

Summatim

Dum interface DRAM non solet primum elementum centrum data considerat cum upgrade exsequens, DDR5 meretur arctiorem aspectum, sicut technologiae promittit potestatem salvam dum valde melioris effectus.

DDR5 technologiam efficere potest quae primos adoptatores adiuvat ad centrum datorum composibilium et scalabilium lepide migrare futurorum.IT et duces negotiatores DDR5 aestimare debent et quomodo et quando ab DDR4 ad DDR5 migrare debent ut eorum notitia media mutationis consilia perficiat.

Post tempus: Dec-15-2022